'Embracing Rather Than Fighting Memory Latency' by Walid Najjar

Stamatis Vassiliadis Symposium

Title: Embracing Rather Than Fighting Memory Latency

Speaker: Walid Najjar, University of California - Riverside, United States

Slides: http://samos-conference.com/Resources...

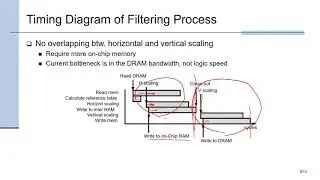

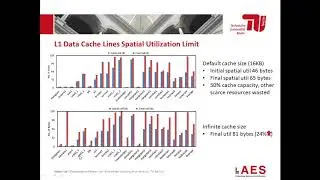

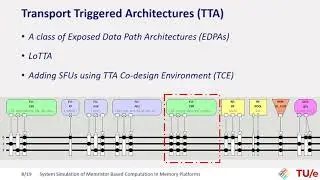

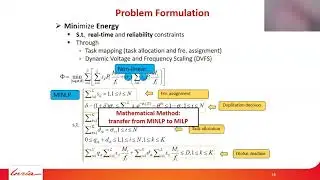

Abstract: Memory latency remains one of the most daunting challenges in computer architecture. Most modern multicore systems mitigate it through the use of massive cache hierarchies that take up over 80% of the chip area and a proportional fraction of its power budget. This approach, however, pre-supposes some form of temporal or spatial locality. A growing fraction of modern workloads, such as databases, data and graph analytics, data mining, bioinformatics, etc, does not exhibit much spatial and/or temporal localities. these workloads are particularly well suited for an alternative solution: latency masking multithreading that trades off memory bandwidth for latency. In this talk I describe how latency masking multithreaded execution on FPGAs can achieve a higher throughput that CPUs and/or GPUs on sparse linear algebra and database operations.

![SLAP HOUSE MAFIA, DKSH, FLOW - BALENCIAGA (REMIX) [NO COPYRIGHT] Car Music 2021](https://images.mixrolikus.cc/video/eJIinxdOOZI)